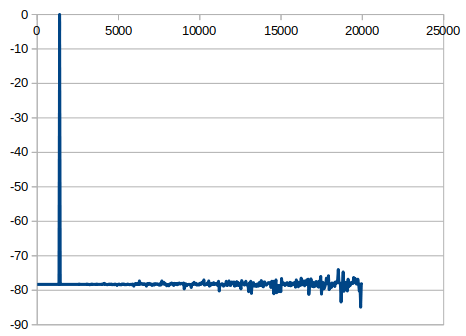

まずはPCM信号

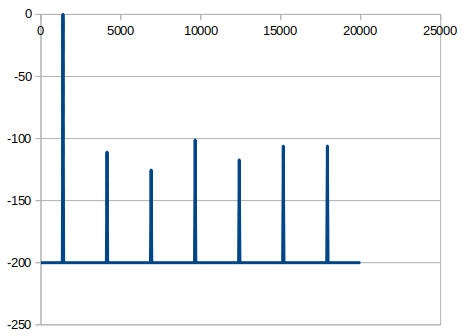

CDDA相当44.1kHz 16bit PCM再生時の周波数別成分分布です。 奇数次の高調波だけが出ています。 3次高調波、5次高調波、…13次高調波まであって、15次は20kHzオーバーなのでありません。

先の説明では、再生方式が持つ理論的上限を確認するため、ハイレゾデータを再生するときのノイズについてシミュレーションしました。 ここでは、CDDAやSACD再生時のノイズについてシミュレーションしてみます。

計算条件

CDDA相当44.1kHz 16bit PCM再生時の周波数別成分分布です。 奇数次の高調波だけが出ています。 3次高調波、5次高調波、…13次高調波まであって、15次は20kHzオーバーなのでありません。

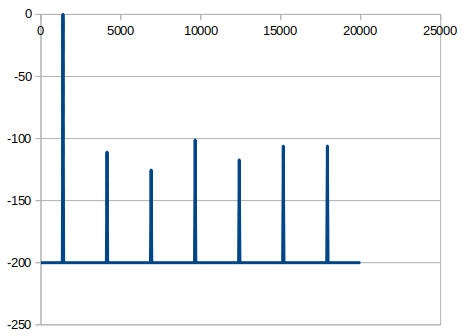

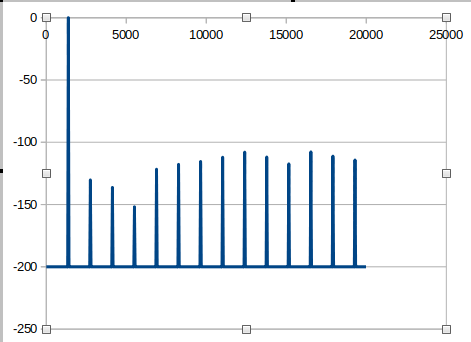

今どき1次の⊿Σ変調器は珍しい方ですね。 WebmasterのPDMアンプにおいて、CDDA入力をFPGAで⊿Σ変調すると、これになります。 再生側のアプリでオーバーサンプリングしてLPFを通すと、S/Nが良くなります。

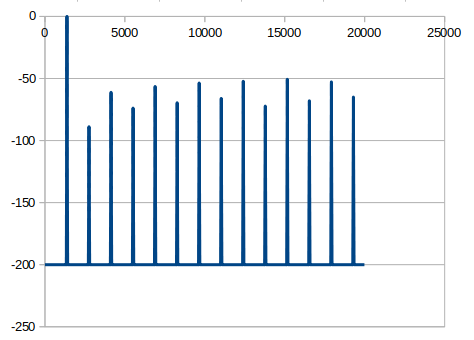

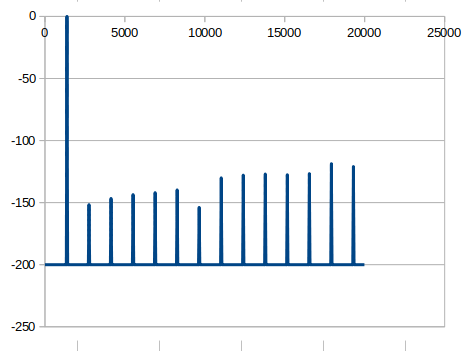

2次の⊿Σ変調器になると、1次変調器よりノイズは減ります。

デジタル音声データの話に書いたように、SACDに入っているDSD信号は⊿Σの最大出力まで振れません。 SACDの出力レベルで、ノイズをシミュレートしてみました。

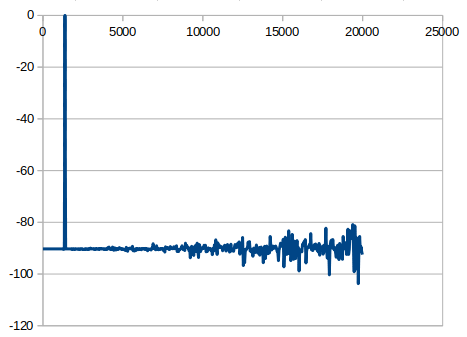

WebmasterのDiscrete DAC出力をシミュレートしてみました。 44.1kHz 24bitのデータを再生したときのシミュレーションです。

ESOTERICのDiscrete DAC出力をシミュレートしてみました。 スペックは公開されていないので、一部想像でパラメータを決めました。 352.8kHzに理想的なフィルターでオーバーサンプリングして、11.2896MHzの8bit⊿Σで出力したところを想定しています。

| 方式 | 全帯域S/N[dB] | ハイレゾ帯域S/N[dB] | 可聴帯域S/N[dB] |

|---|---|---|---|

| PCM | -24.9 | -27.0 | -98.0 |

| 1次⊿Σ | 0.0 | -37.1 | -45.5 |

| 2次⊿Σ | 8.45 | -51.0 | -63.0 |

| 2次Δ∑ DSD | 11.2 | -46.0 | -51.5 |

| 8bit ⊿Σ | -36.5 | -92.1 | -101.9 |

| ESOTERIC方式を想定 | -46.3 | -103.8 | -115.2 |

S/Nと書いていますが、すべての値はノイズ量を信号強度で割った値です。 ノイズが少なければ、値も小さくなります。

Webmasterが最初にDSDの仕様を聞いた時、「それでCDDAの解像度を超えられるの?」とシンプルな疑問を持ちました。

サンプリング周波数を上げたときデータ1とデータ0を交互に出して、ローパスフィルターを通せば0.5を出力できます。 データビット長を拡張するのと同じ効果があります。

でもサンプリング周波数を2倍にしても、ビット長を1ビット加えたのと同じ効果です。 SACDのDSDはCDDAの64倍ですから、ビット長増加効果は6bit分です。 DSDの1bitに6bitを足しても7bitにしかなりません。 実際には、ノイズシェーピングも解像度追加の効果がありますが、数値的に計算することができません。 しかもSACDは50kHzまでの信号を再生しますから、ビット長拡張効果が減ってしまいます。

今回計算した結果では、2.8224MHzの2次⊿Σ変調器で50kHzまでの信号を格納するとS/Nが-51dBです。 ビット長相当に変換すると6dBが約1bit分なので、8.5bit分ですね。 SACDプレーヤーのカタログには理論S/Nが-140dBとか書いてありますけど、本当ですかね。 ⊿Σ変調器を2次から7次にすることでさらにS/Nが稼げるとは思いますが、90dBも改善はできないでしょう。 しかも、DSD信号は信号レベルを低く抑える規制が入っているので、⊿Σ変調の最大振幅までは使いません。

WebmasterはS/Nが-51dBでも低すぎるとは思いません。 アナログレコードのノイズレベルを測定したら-30dBでした。 でもスピーカーでアナログレコードを再生して、不満は感じません。 -51dBでも、ハイファイ再生には十分だと思います。 また、CDDAの再生を突き詰めると、SACDよりも解像度が上がるはずです。

Webmasterの特許方式でスピーカーをPDM駆動した時、今の実装ではCDDA再生時のS/Nが-45.5dBです。

数値至上主義者から見ると許せないS/Nかもしれませんが、やはりアナログレコードのS/Nを超えています。 スピーカー駆動には十分なS/Nが稼げていると思います。 同時に、CDDAの解像度を全部は活かせていないのも確かです。

PDM駆動の主目標はスピーカーの精密駆動ですから、-45.5dBの限界S/Nに近いところまでスピーカーを駆動できているはずです。 PDM駆動を超えるには、-45.5dBを超えるアナログスピーカー駆動方式を用意しなければなりません。 電圧駆動のアンプには負ける気がしません。

最近(2024年現在)Webmasterが試しているのが、ディスクリートDACです。 理想的な電流駆動アナログアンプが用意できたとして、どうしたら高精度のD/A変換ができるかという問題です。

Webmasterの10年以上前から、様々な自作派が試してきましたし、現在ではメーカーも手を出しています。 主流は2方式あります。 1bit⊿Σ信号を過去数bit分並べて、移動平均を取る方式が一つ。 マルチビット信号をラダー抵抗でD/A変換する方法がもう一つ。

Webmasterは1bitの移動平均方式には興味がありません。 移動平均方式でできることは、1bit信号を精密にアナログ化することであり、1bit信号方式が持っている限界を超えることはできないのです。 CDDAを2.8224MHzの1bit信号に2次変調器で変調したら、限界は-63dBです。 11.2896MHzの1bit信号にして、ようやく-101.5dBです。 CDDAをなんとか超えましたし、ピアニッシモではS/Nが信号強度の減り方以上に劣化します。

ラダー抵抗方式にも弱点があります。 抵抗素子に誤差があることです。 秋葉原で普通に買える高精度抵抗は誤差0.1%です。 1/1000ですからbit長に換算すると、10bitです。

単純にPCMをラダー抵抗で変換するには10bitの精度しか出せません。 そこで使えるのが⊿Σです。 変換できなかった下位bitの情報をノイズシェーピングで表現します。 FPGAを使えば、CDDAをもっと高い周波数で⊿Σ変調できます。

この発想でwebmasterが試作したのが、8bit⊿ΣのディスクリートDACです。 10bitではなくて8bitに抑えてあるのは理由があります。 ⊿Σでノイズシェーピングすると、出力データの最下位にデータの1を足したり足さなかったりします。 この1の精度が重要なのです。 10bitの⊿Σにすると、最下位データの1には、同じ値の抵抗値誤差が含まれます。 誤差±100%ということです。 これではノイズシェーピングの効果が半減です。 8bit出力に抑えておけば、最下位データの1が含む誤差は±25%です。

2024年3月20日 初出

2024年3月21日 追記