現在位置のナビ

トップ → コンピュータの国 → 雑記帳 → 趣味趣味音響 → 電流駆動アンプ回路案

説明

純粋電流駆動アンプの回路を考えてみました。

実装と試験はしていないので、実際に作ると発振したり不具合が出るかも知れません。

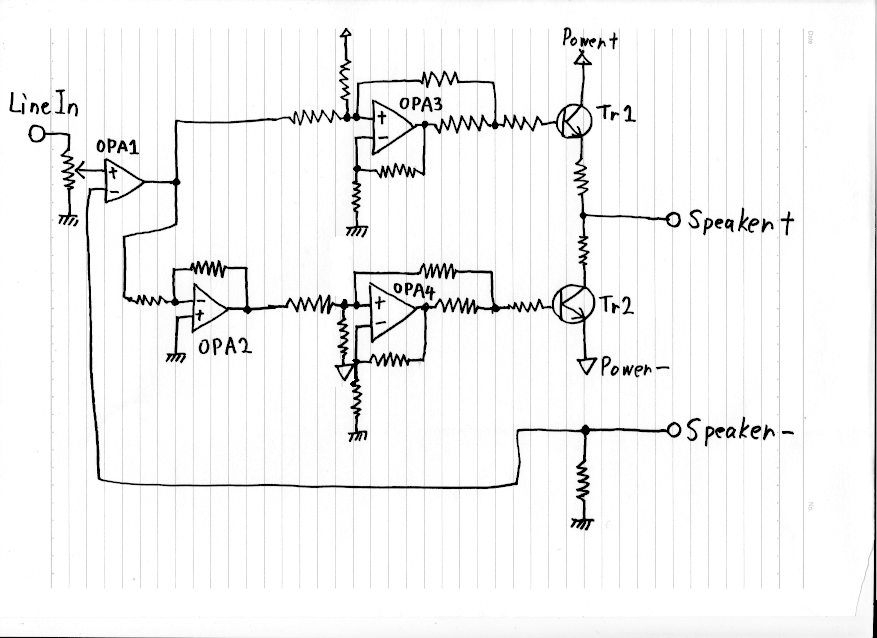

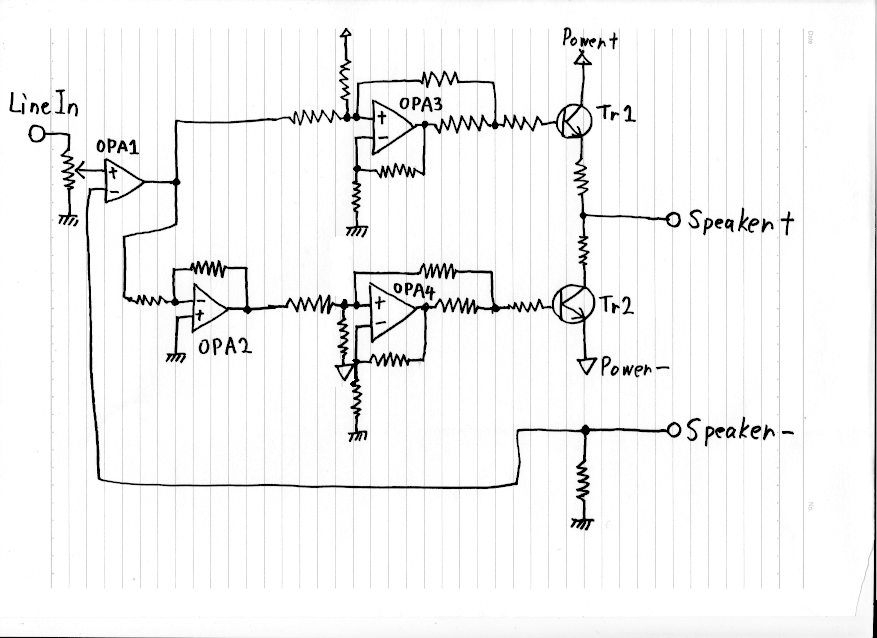

回路例1

図1 電圧入力、電流駆動アンプ

図1 電圧入力、電流駆動アンプ

図1が、目的の回路です。

最終段は電流出力なので、FETではなくバイポーラトランジスタを使用してSEPP回路にします。

出力電流0付近にギャップを作りたくないのでAB級駆動します。

全体に電流NFBがかかっているので、SEPPはコンプリメンタリなTrでなくても大丈夫でしょう。

出力電圧の辻褄合わせは、抵抗とTrで行うので、Trは大きく発熱しそうです。

OPA3とOPA4は電圧入力を電流出力に変換する同じ回路です。

最終段をAB級駆動するための入力電圧オフセットがかかっています。

電流引き込み用のTr2を負電圧入力のときに駆動するため、OPA2が電圧反転しています。

OPA1は入力とNFB電圧から、増幅段を駆動するOPアンプです。

OPA1とOPA2は、必ずGNDに対する正負電源が必要になりますが、それ以降を単一DC電源で駆動する回路に改造できそうですね。

2019年9月8日 追記

OPA4の入力にかかるDCオフセットを、プルアップからプルダウンに変更しました。

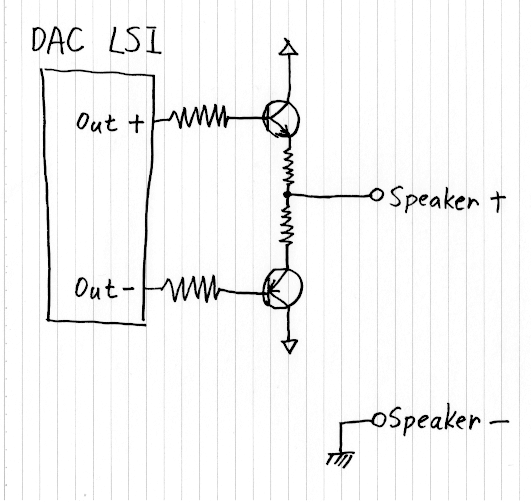

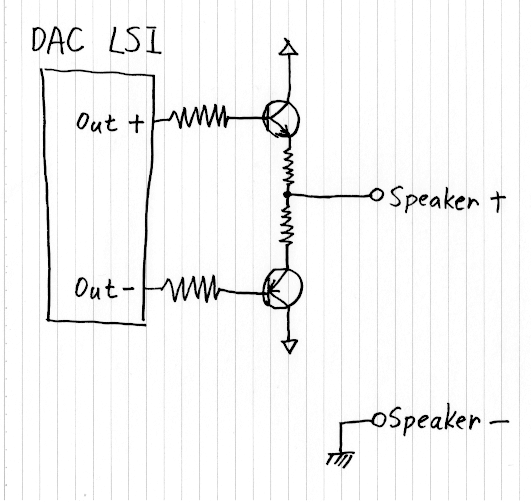

回路例2

図2 電流出力のDAC LSIから電流駆動する

図2 電流出力のDAC LSIから電流駆動する

図2は、電流出力のDAC LSIから電流駆動しています。

バイポーラトランジスタが入力電流に比例した電流を流しています。

ボリューム調節はどうしましょうか?

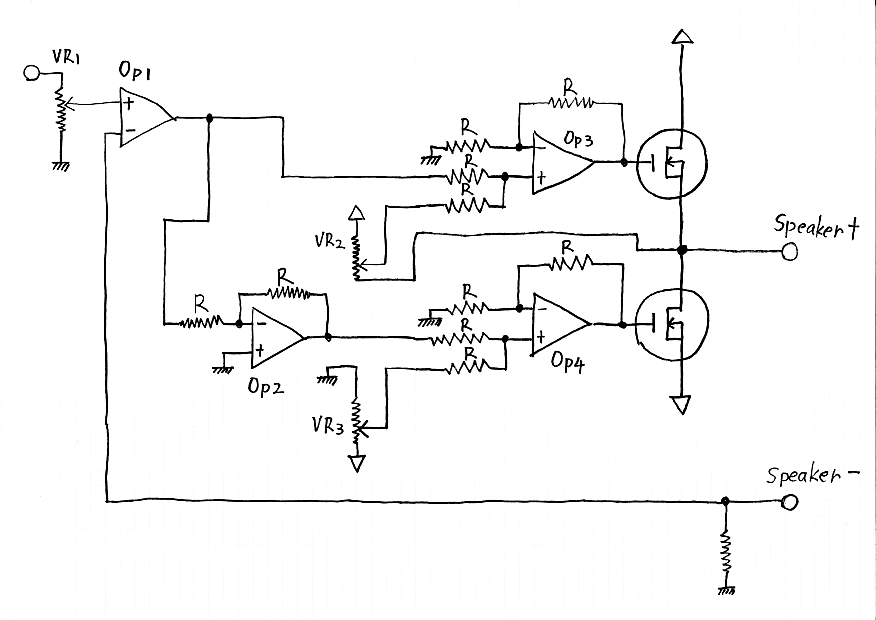

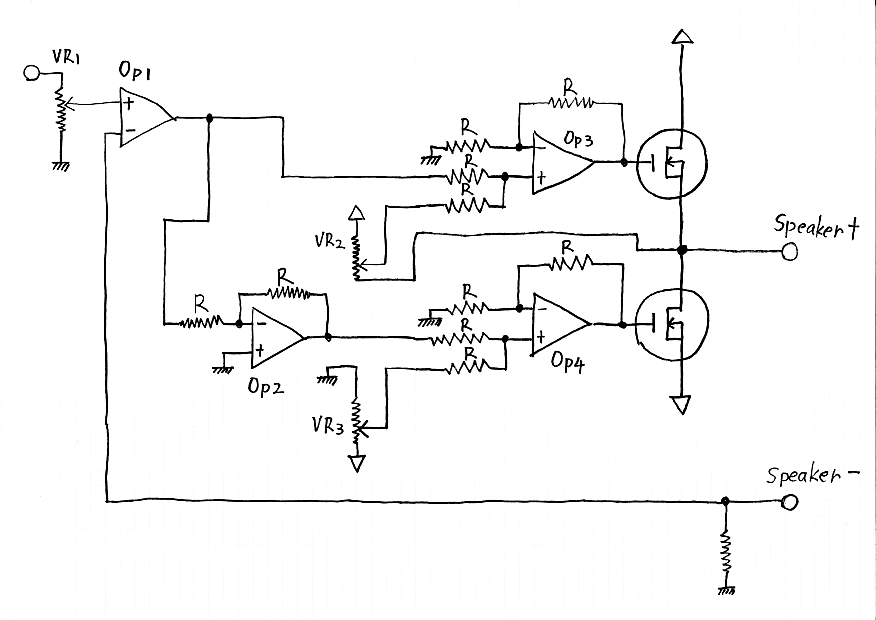

回路例3

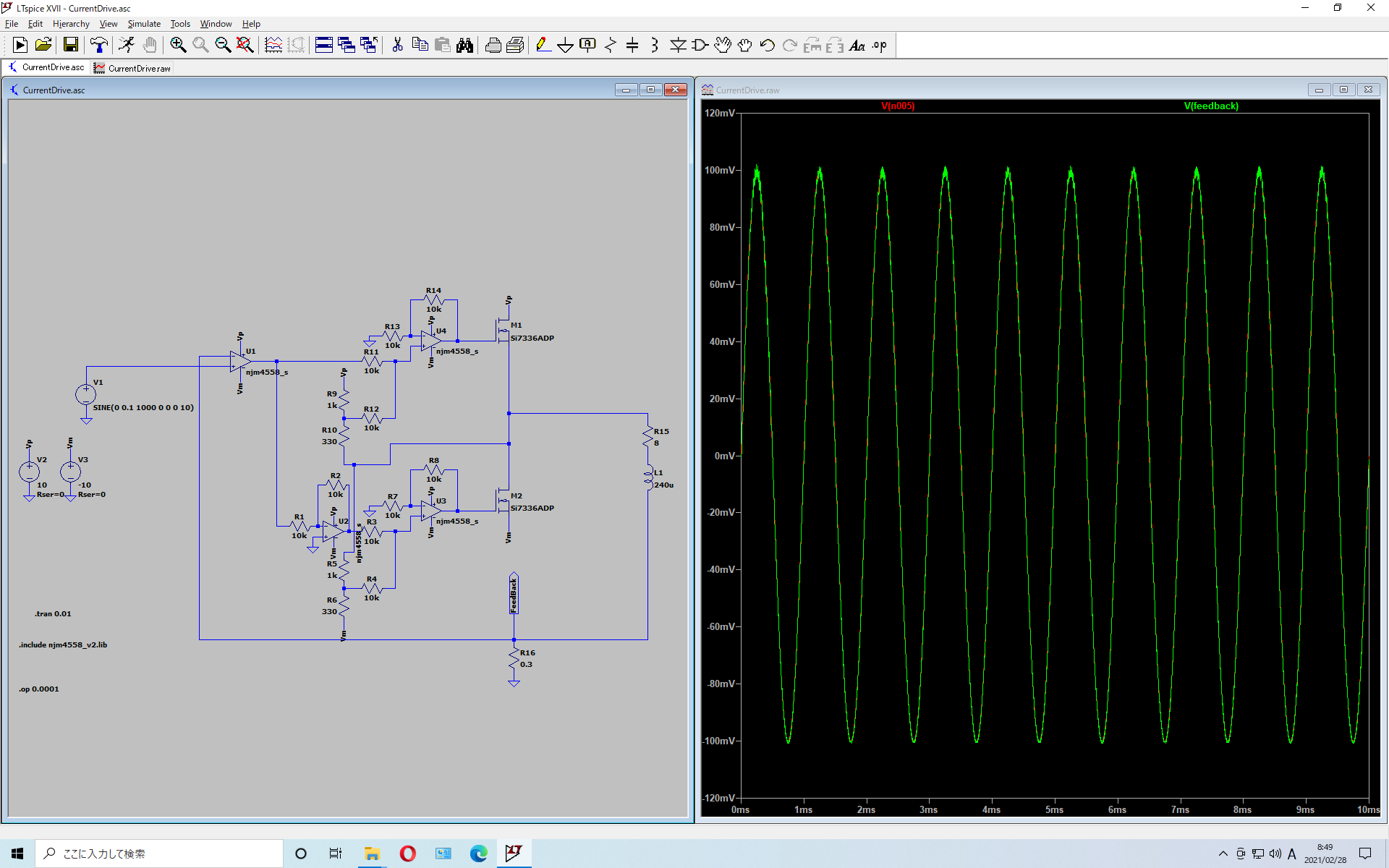

図3 電圧入力、電流駆動アンプFET

図3 電圧入力、電流駆動アンプFET

図3は、最終段をFETにしてみました。

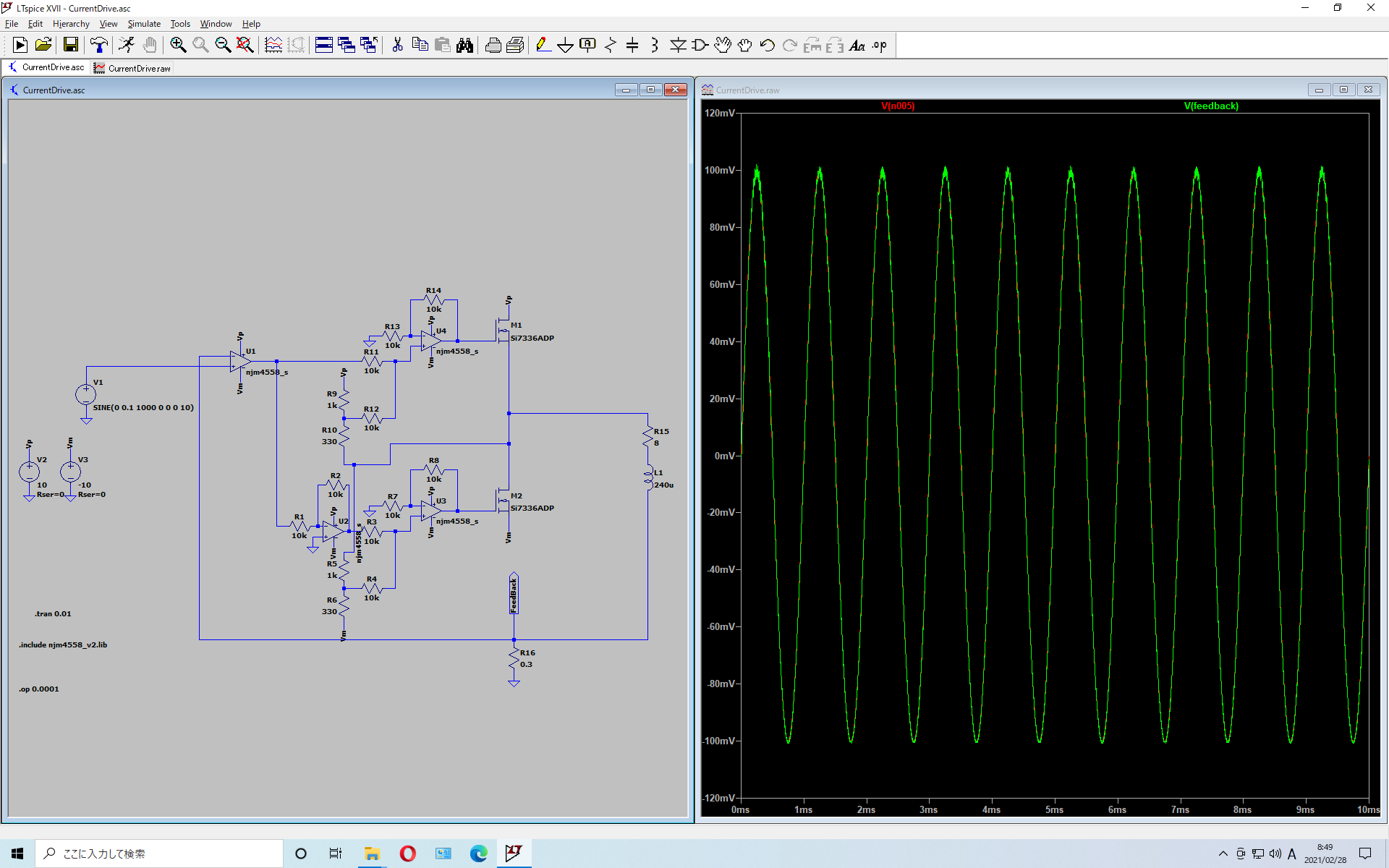

LTSpiceでシミュレーションしてみました。

図3B LTSpice実行結果

図3B LTSpice実行結果

画像は縮小表示しています。

PNGファイルを手元にコピーしたら、拡大表示して細部も読めます。

1kHz入力と電流帰還電圧を重ねて表示していますが、ほとんど同じグラフです。

2つのFETが同時に動作するA級動作では、フィードバックループの遅延で発振していますが、発散はしません。

FETの型番は、LTSpiceの操作でリストのトップにあったNMOSを選択しています。

FETとOPアンプを変更すると、発振の具合も変化します。

こんど秋葉原に行った時に、部品を買って試作してみます。

2021年8月26日追記

回路は既に組み上げました。

期待通りに動作しないのでデバッグ中です。

デバッグに使うファンクションジェネレータがないので、プログラムとUSB DACで代用したり、オシロスコープの表示に使っていたパソコンが壊れたり、オシロスコープのプローブが大きすぎて回路にあてられなかったりするので、作業は進んでいません。

ハードウェア作業のあるあるですね。

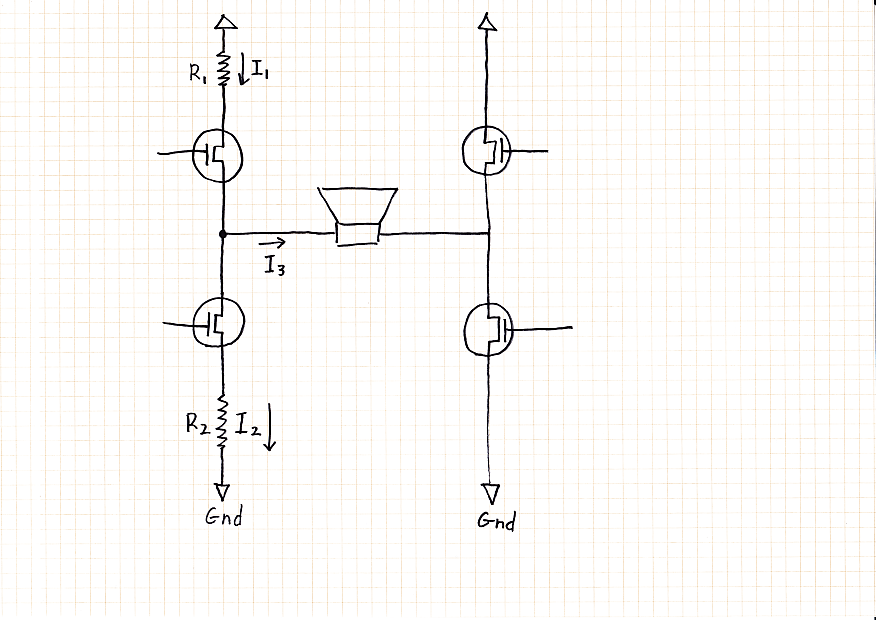

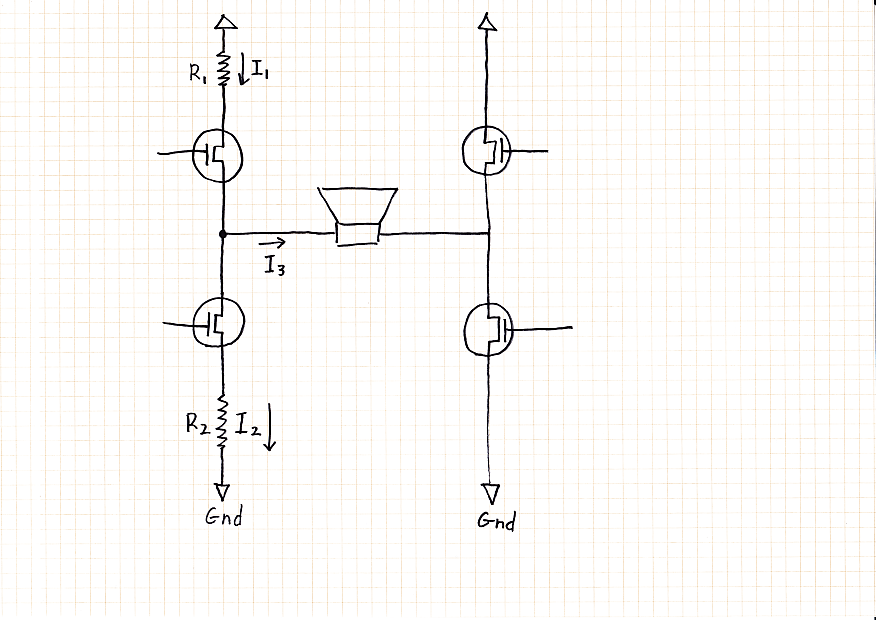

回路例4

図4 電圧入力、電流駆動BTLアンプFET

図4 電圧入力、電流駆動BTLアンプFET

図4は、単一電源でBTL駆動のFETにしてみました。

半導体メーカーが本気を出せば、ワンチップにできます。

モーターをPWM駆動するフルブリッジ回路を応用し、アナログ駆動します。

各FETを駆動する電圧は、図3の回路の応用で作れます。

R1とR2は電流測定用の抵抗です。

I3 = I1 - I2 です。

2020年9月6日追記 実装準備をしています

回路例1を実装するため、助っ人を頼みました。

トラ技のLV1.0でヘッドフォンアンプ回路を設計した川田章弘氏です。

Trの部品選定と、各所抵抗値の決定をお願いしました。

8月3日に引き受けてくださったので、そろそろ設計が終わっている頃でしょう。

2023年3月20日の状況

読者から進捗をきかれました。

川田氏からは、連絡が途絶えました。

自分で回路例3を2回実装したのですが、音が出てきません。

FETのバイアス値の不整合を疑っているのですが、これ以上はオシロスコープが必要になります。

PDMアンプの試作を優先しているので、そちらが一段落したら戻ってきます。