経過報告

『お気楽オーディオ』の藤原氏からAK5572キットを購入しました。 48pin QFNパッケージのはんだ付けに頭を抱えています。

水晶発振器のEPSON SG8002のDIPパッケージがいつの間にかディスコンになっていますね。 水晶発振器の入手先を探さないといけません。 試作品には、昔の試作基板から発振器を抜いて使います。

Tang Nano 9kでトラブル

FPGAとしてTang Nano 9kを使おうとしているのですが、コンフィグレーションできません。 まず、書き込みに失敗します。

サンプルでさえ、内蔵フラッシュROMに書き込もうとするとエラーになります。

LinuxでもWindowsでもSRAMに書き込めてフラッシュROMに書き込めません。

openFPGALoaderも試しましたが、ダメでした。

複雑なコンフィグレーションは、SRAMに書き込めても正しく動作しません。 Tang Nano 1k と Tang Primer で動作したVerilog HDL なので、HDL自体には問題ないはずです。

Tang Nano 9k は3個購入したのですが、全部同じ症状です。

2024年10月末にGoWin IDE を配布しているGoWin semi社に報告済みです。

進捗状況の問い合わせは、ご遠慮ください。 言われなくてもコツコツやっているか、どこかでハマっています。 作業協力は歓迎します。 「自分の会社でキット化したい」という会社さんがあれば、今交渉中のところから乗り換えるかもしれません。

2024年11月6日追記

Tang Nano 9kに複雑なコンフィグレーションができなかった理由がわかりました。 開発ツールのGoWin IDEでVerilog HDLの解釈が変わっています。 古いバージョンで動作したHDLが新しいバージョンで動作しなくなっているので、Verilog HDL を書き直しました。 現状、SRAMで動作しています。 GoWin Programmerから内蔵Flash ROMに書き込めない状況は、変わりません。

Linux上の openFPGALoder v0.12.1 の -f オプションでFlash ROMに書き込めました。

2024年11月8日追記

GoWinから返答がきました。 最新版のProgrammerでTangNano9kに書き込みできないバグがあるそうです。 現在対応中なので、古いProgrammerを使ってほしいということでした。

2025年4月2日追記

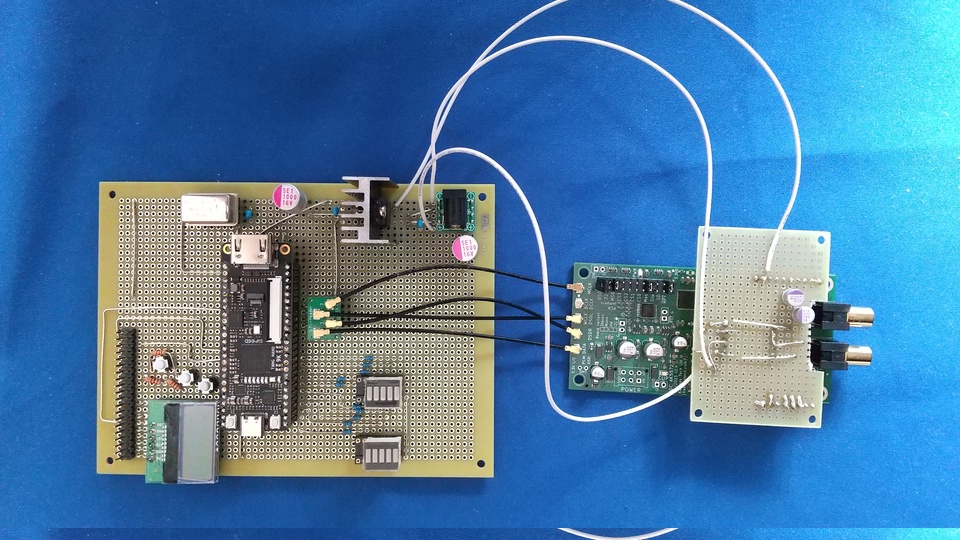

第1試作が動作しました。 お気楽オーディオのキットはADCチップのハンダ付けがうまく行かないので、 Kaamostech の完成基板を使いました。

352.8kHzfsのPCMのふりをして11.2MHzの⊿Σ2chを入力しています。 レベルメーターもあります。 モニター用のヘッドフォンアンプも企画したのですが、基板サイズの関係で載せられませんでした。

2025年9月13日追記

第1試作は快調動作しています。

プロジェクトの公表段取りが遅れ気味です。 キット化の手配が進んでいません。 どうせ、オーディオメーカーからの横槍でしょう。

㈱KORGとTEAC㈱は、自社のWEBサイトでwebmasterの嫌味を書いてくれたことがありますから、怪しい会社の筆頭です。 それぞれ、USB接続の⊿Σ録音ADC商品を持っていますし。

技術詳細の発表を、2026年前半目標で進めているところです。

2025年11月27日追記

プロジェクトは止まっています。 2026年前半公開の予定も怪しくなってきました。

業界の怪しい動きを見つけました。 2025年6月には、11.2MHzの⊿ΣをUSB経由で録音する技術は、日本国内には某社が外注に作らせた一つしかありませんでした。 2025年11月現在、インターフェイス株式会社のWEBサイトを見ると、DSD 11.2MHz対応の ITF-USB DSD RECを宣伝しています。

おそらく、このインターフェースを使って11.2MHz⊿Σ録音機を設計している会社があって、こちらのプロジェクトを止めるよう圧力をかけているのだと思います。