現在位置のナビ

トップ → コンピュータの国 → ハードウェア → Discrete DAC 設計資料

説明

8bit ⊿ΣのDiscrete DACを作りました。

制作過程とちょっとした感想は こちらに書いてあります。

読者でもクローンが作れるように、設計資料一式をここで公開します。

設計データの取扱

ここで公開したデータは、自由に再利用していただいてかまいません。

自分でクローンを作っても良いですし、キットとして売り出してもかまいません。

回路を変更するのも自由です。

ただし、他者の権利を侵害していないかどうかは保証しません。

その他、何も保証しません。

設計データを再掲載する場合は、オリジナルを公開しているこの場所を紹介してください。

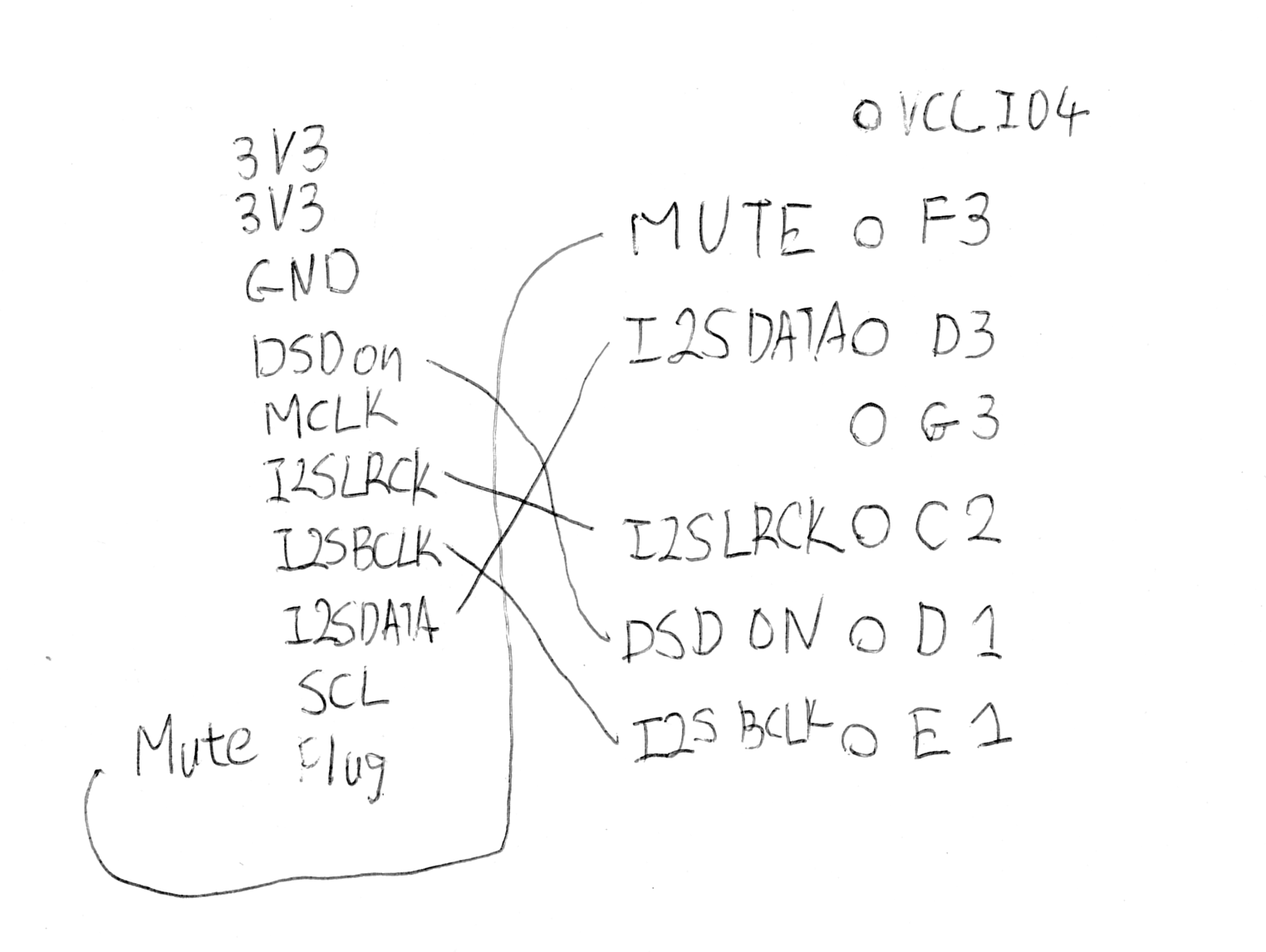

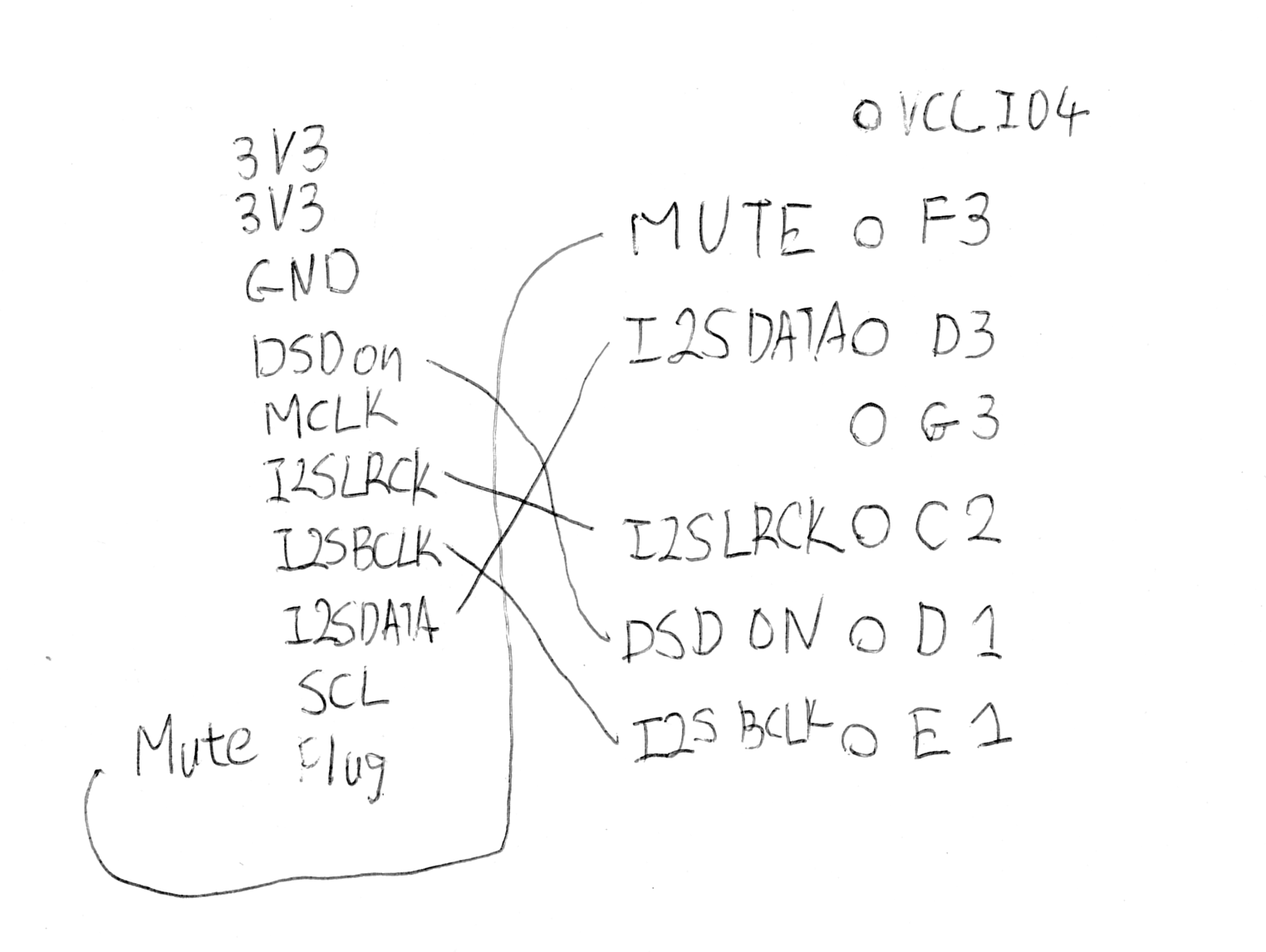

Mach XO3との接続

Mach XO3のコンフィグレーション

以下のファイルを展開して、ツール"diamond"でMachXO3L starter kitのフラッシュROMに書き込んでください。

Webmasterが使ったdiamondのバージョンは、"3.10.0.111.2"です。

DiscreteDAC.zip

XMOSとの接続

GNDと信号線5本を接続しています。

| XMOS側信号 | XO3側ピン |

|---|

| I2S data | D3 |

| I2S bit clock | E1 |

| I2S lrck | C2 |

| DSD on | D1 |

| mute | F3 |

図1 XMOSとFPGAの接続

図1 XMOSとFPGAの接続

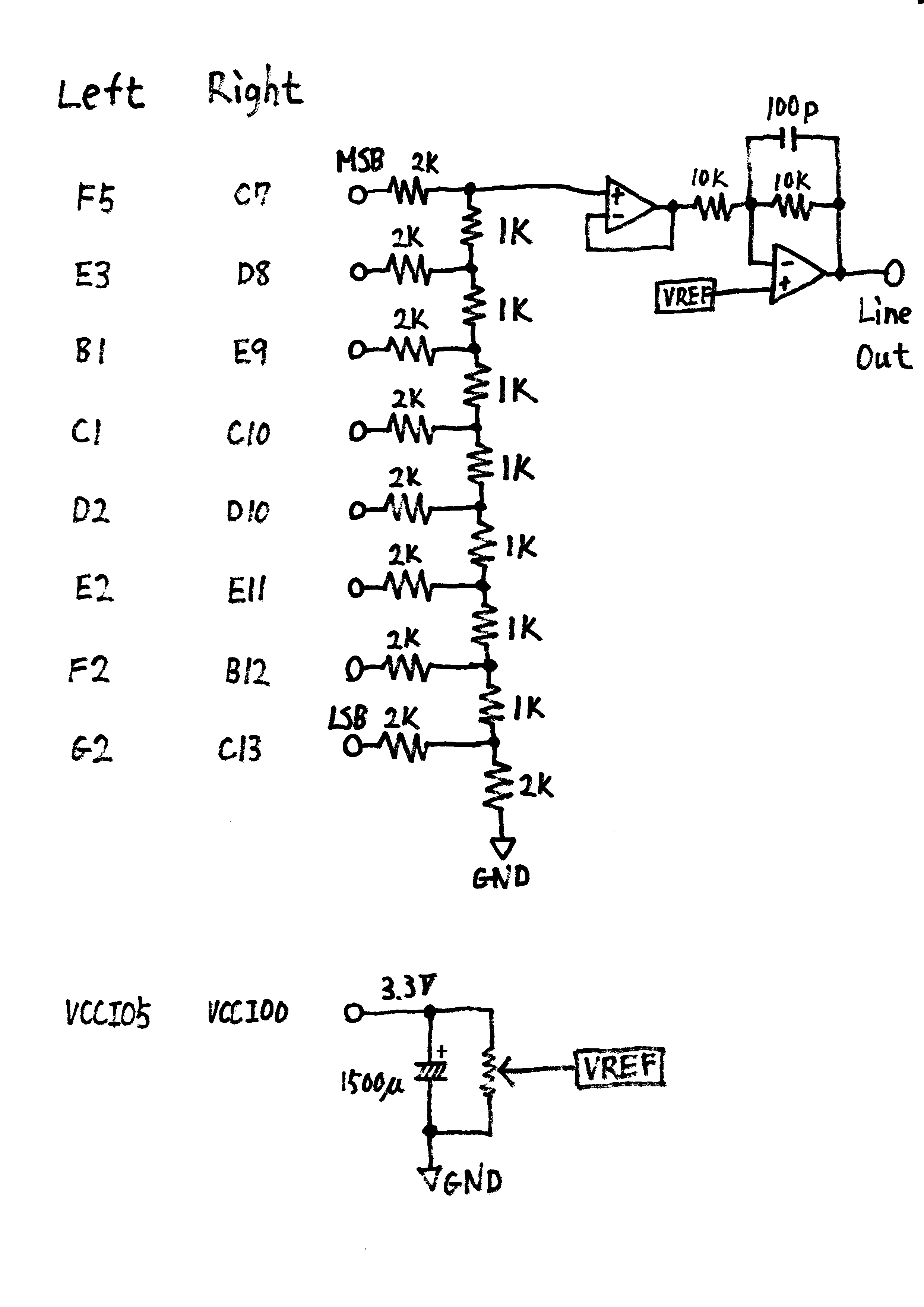

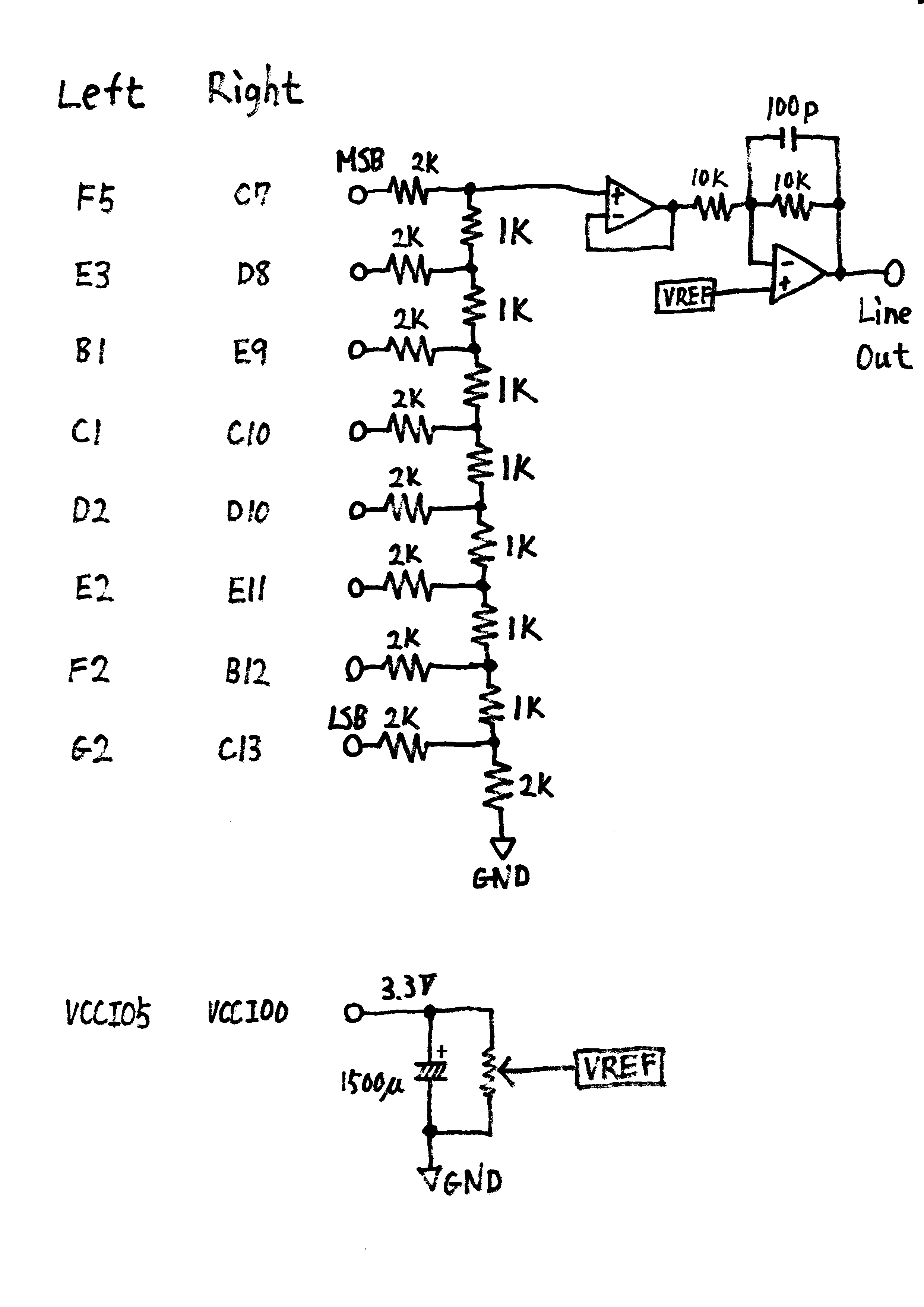

アナログ回路との接続

以下の回路図を参考にしてください。

評価基板には2x20のピンヘッダを4箇所に取り付けることができます。

今回は外側の2組だけを使う設定にしました。

図2 アナログ部分回路図

図2 アナログ部分回路図

Mach XO3の電源

USBミニB端子からVBUSの5Vを供給しています。

オンボードの3.3V LDOを使用するのに、これ以外の電源端子が見つからなかったからです。

オンボードのLDOを使わなければ、外部から3.3Vを供給してもかまいません。

Verilog HDLの注意

DS31STATE.vには、全く同じ構成のモジュールが2つ定義されています。

最初は一つのモジュール定義で2つ実装しようとしたのですが、diamondのバグで「信号線名がダブっている」という意味のエラーになったので、2つ定義しました。

2024年12月15日追記

Verilog HDLのソースコードにバグがありました。

モジュール使用の書式を間違えていたので、2つのモジュールが使えなかったのでした。

書き直したので、今度は大丈夫です。

ZIPファイルも置き換えました。

アナログ回路

OPアンプはOPA2134を推奨します。

ラダー抵抗は誤差0.1%の抵抗を使用してください。

2段めのOPアンプ回路は反転出力になっています。

この回路通りに作ると、プラス入力でライン出力はマイナスになります。

気になる人は、もう1段反転回路を入れてください。

ラダー抵抗から出てくる出力信号は、20kHzオーバーのノイズを大量に含んでいます。

回路図のアナログ回路では、ノイズの減衰が不十分です。

スーパーツイーターなどを接続したら、大量のノイズを再生することになってしまいます。

気になる人は、アナログ回路に遮断特性の良いLPFを組み込んでください。

回路が組み上がったら、PCMのゼロを連続入力して、出力レベルがほぼ0Vになるように半固定抵抗を調節してください。

FPGA実費で提供可能

コンフィグレーションが終了したFPGAを希望する人には、MachXO3L Starter Kitに書き込んだ状態で提供することもできます。

アバウトに実費で提供します。

2024年5月現在でDigiKeyから取り寄せるとして、2週間の期間と1万円くらいの費用でできます。

ご希望の方は webmasterまでメールしてください。

2024年5月14日追記

今DigiKeyを見ているのですが、MachXO3L評価基板が25,000円超えています。

実費の提供費も高くなります。

FPGAの初期化

FPGA の動作では、音出しをする前に最低1回のMuteパルスかPCM/⊿Σ切り替えが必要になります。

WebmasterはLinuxから使っているので、USBケーブルをつなぐ前にFPGAの電源が入れば問題ありません。

USBケーブルを繋ぎっぱなしにしている人とか、Windowsに接続する人は、一旦PCM/⊿Σのモードを切り替えてから本格的な音出しをしてください。